SI部分工作的起端比较单一,同时也缺乏理论基础。第一篇就从基础开始,重新梳理一遍。夯实基础后再回头总结工作。本文参考两本书籍:Eric Bogatin的《信号完整性与电源完整性分析》和陈兰兵的《Cadence高速电路设计 Allegro Sigrity SI/PI/EMI设计指南》。

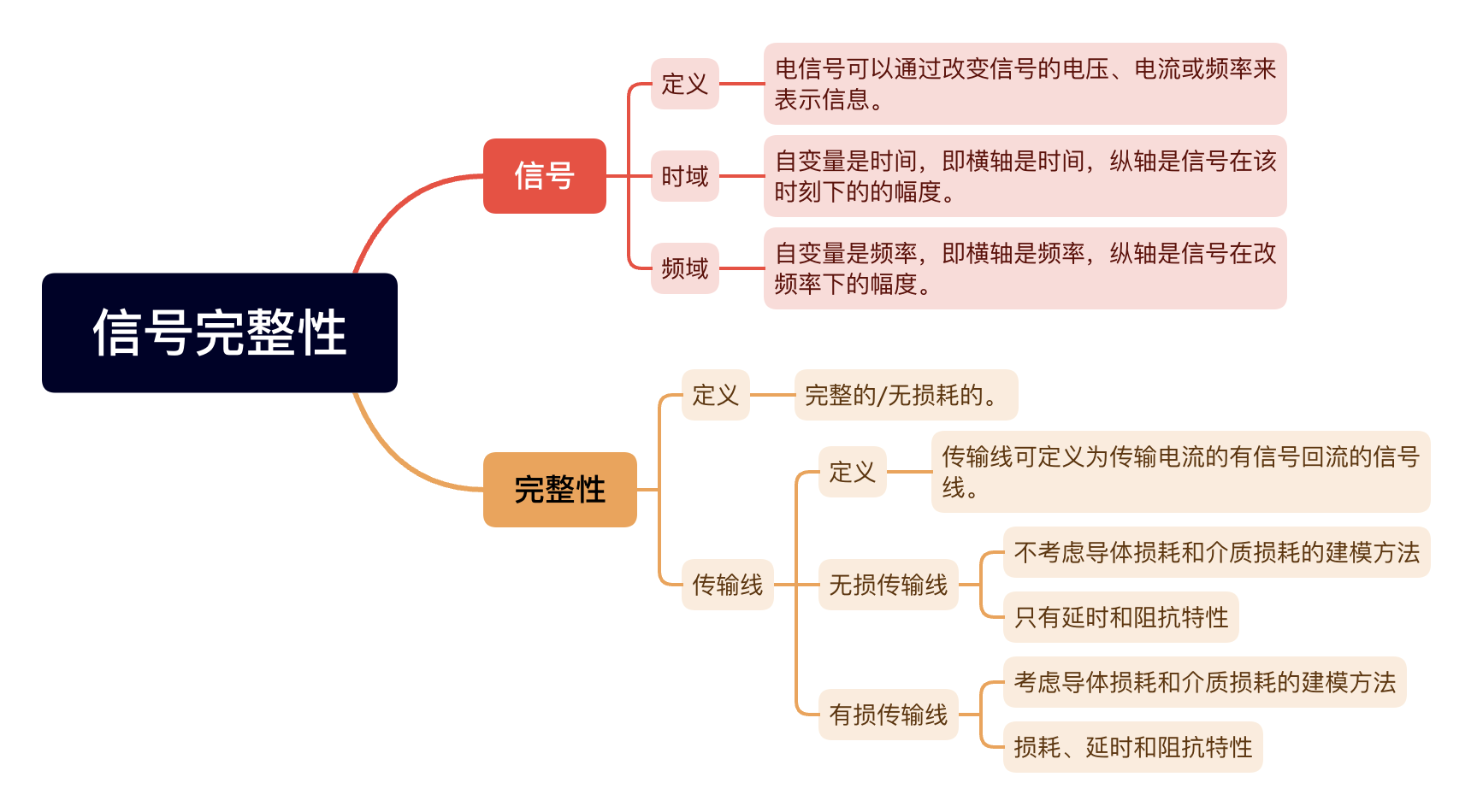

一、从要研究什么问题开始。先把书读薄,信号完整性问题就是要研究怎么把“信号”“完整的、无损耗的”从源端传输到终端。这个定义过于严苛,现实世界中不可能做到无损耗,完整的倒是有可能。理解起来损耗要做到可接受的范围内,才能保证信号“完整的”传输。有点类似于PI的目的,把电源通过PDN“完整的”传输。信号是将PDN替换为了传输线。

书中提到基本的电阻、电容和电感的物理基础,主要是为了引申出“传输线”的物理基础。从PCB设计的角度上来看,传输线就是指PCB走线。但是又不仅仅是PCB走线,还包含了信号的回流路径及介质(在看串扰时还有相邻传输线)。

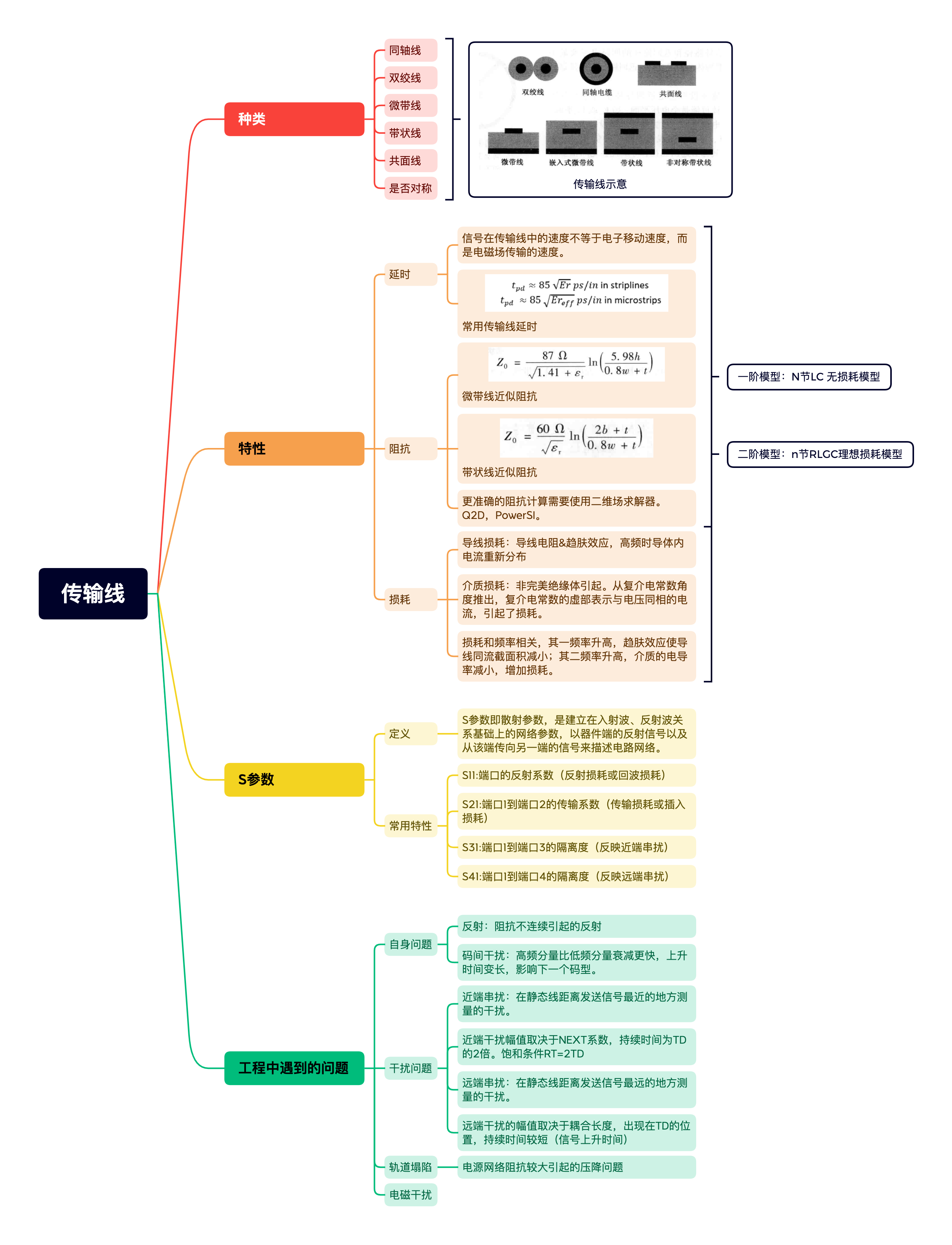

二、传输线:

从Eric Bogatin的书中我整理出了关于传输线最浓缩的部分,理论和公式的推导不搬运了。传输线理解起来就是信号的频率高了,不能再认为铜皮就是电阻,需要考虑不同信号频率下的损耗和传输,甚至需要将铜皮的粗糙度、过孔残桩及连接拓扑也考虑在内。

根据影响传输线的介质特性-介电常数可以得出的一个经验,越高频率的信号越需要低介电常数的板材来制作,尝试使用Saturn计算一下同样的叠层下50ohm的传输线的差异。数据中可以看出同阻抗下低介电常数的材料可以实现更宽的走线(更低的寄生电感),以及更低的寄生电容,从而使高频下的信号衰减更低。

关于传输线总结一下几点:

1、需要理解阻抗在其中的作用,做好阻抗匹配是无损传输信号的前提。(PCB线路阻抗仿真-留坑)。

2、在应用中需要考虑不同情况下的传输线延时,例如在表层和内层的延时差异。(PCB走线延时仿真@DRAM时序-留坑)

3、串扰的问题在工程中给出经验,增加间距,减小耦合长度。3W(70%)5W(98%)。(PCB走线串扰仿真-留坑)

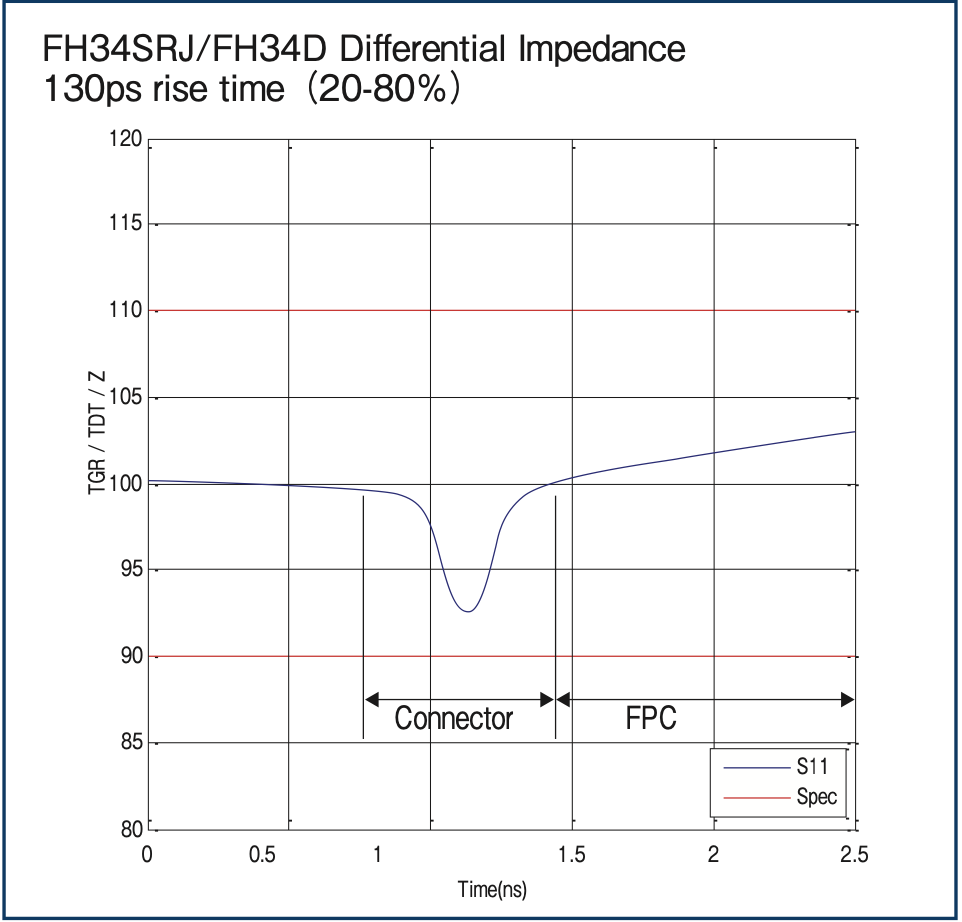

写在最后,在华为信号完整性的部门叫“互联部”,Die和Package的互联,芯片的互联,PCBA之间的互联都有涉及到信号完整性的部分。写到这里让我想起了一个刚开始工作中遇到的实际案例,当年有一个产品因结构原因无法在主板放下一个USB3.0的连接器,需要通过FPC转接到另外一个子卡上,起初选择了Hirose的FH34系列连接器,下图为Spec中的阻抗跳变不超过10%;

产品中期成本核算发现Hirose的连接器成本过高,供应链同事建议更换为ECT同款的连接器,但是未进行全面的评估和测试。结果回板后发现USB3.0测试不通过,仅能工作在USB2.0。幸好更换节点不在量产中,否则一批PCBA都要报废了。以此为鉴,高速信号需要更全面的考虑影响因素(走过的路径都有可能会让信号质量变差)。除此之外还有好几个关于SI的例子。所以更重要的工程中掌握仿真工具,能更全面的验证设计。

结束。