从第一个项目说起,Q公司的项目。起初公司的项目是ODM完成的,PI自然就成了只需要检查的一部分。随着公司产品的成熟硬件平台自研的需求来了。从SOC平台的设计上分工:DRAM没有工作量(POP封装)、PMIC+GPIO分配、外围的几个模块都有同事负责了,只剩下了PI这一个大家都没有搞过的部分了,我自告奋勇接下了这部分工作。

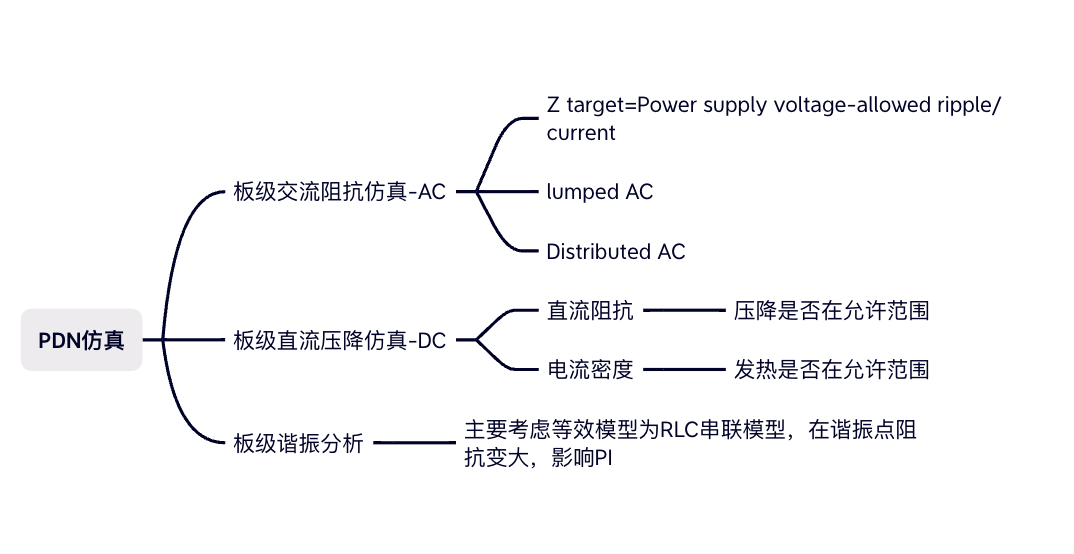

一、拿到任务,先想想怎么拆解开,把一个复杂问题化解为多个小问题:PDN仿真部分的工作可以分成AC和DC两部分;其中AC分为lumped和distributed两部分。

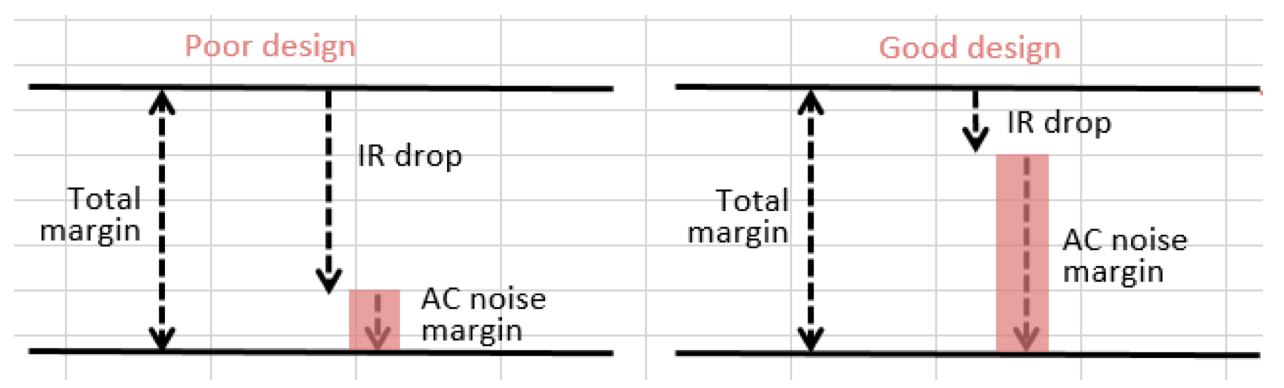

拆分完任务,开始了第一个思考,AC和DC之间的相互作用是什么?从下面的图中可以看到Spec中常看到的Vmin和Vmax组成了Total margin,AC和DC各负责一部分,总体不超出Spec的限制即可。

图一 Voltage margin

图一 Voltage margin

二、那就先从简单的DC部分开始,看板级的DC压降设计和以往layout的时候看线宽铜厚以及过孔的数量确定通流能力的原理一致(IPC-2152 PCB通流能力-留坑①),只是在SOC的设计中密度提高了,无数的过孔将平面变成了筛子。仿真软件能更快速的统计出结果,且直观的展示出来。当PCB的器件密度变高的时候还需要关注另一个电流密度的参数和发热情况。

大部分的情况对PI有要求的芯片都会给出详细的DC阻抗要求,这时候只需要对相应的网络进行仿真就可以了。也会有SOC给出IR Drop的要求,常用的仿真软件都会集成相应的功能模块,比如Sigrity PowerDC(PowerDC仿真步骤-留坑②)。

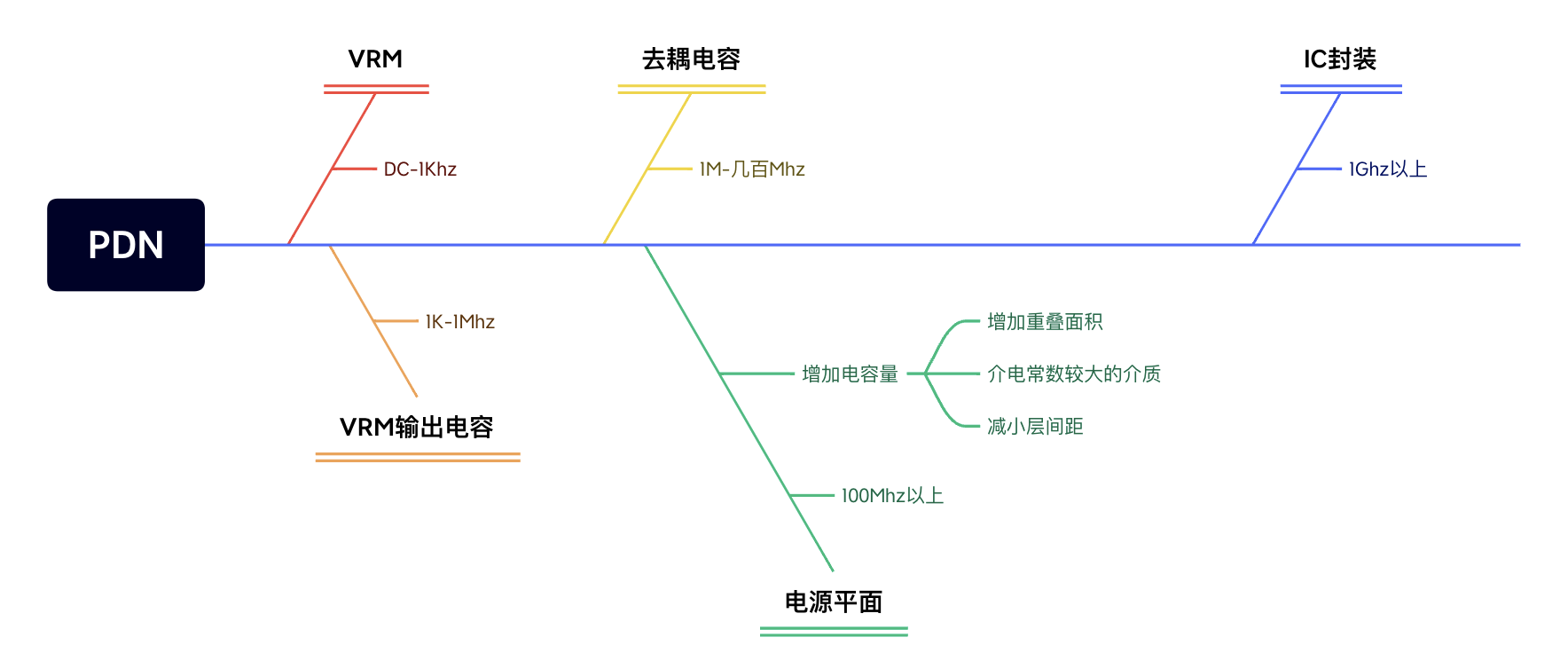

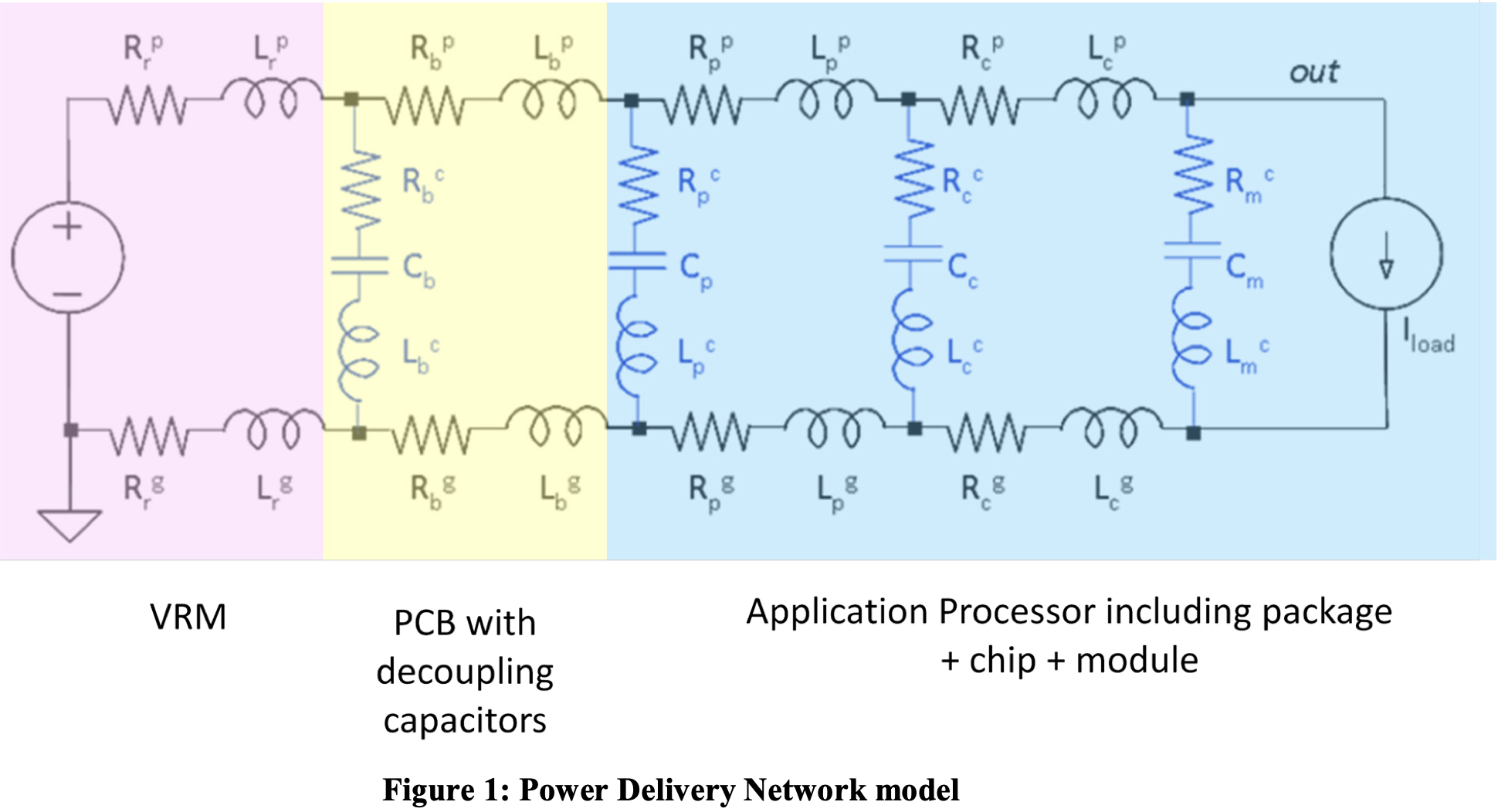

三、AC的部分理解起来需要增加一个频率的维度,也就是不能再把PCB上的铜皮理解为一个电阻使用欧姆定律来看设计的好坏了。这时候引入PDN的组成部分能更好的理解设计的目的。

图二 PDN网络组成

图二 PDN网络组成

从PCB的角度上看有三个部分:VRM、电容和PCB。VRM的电源完整性是一个很大的话题,从长计议(后面再写DCDC的文章③)。在SOC的设计中我们只看电容和PCB,把VRM假想成理想源,于是我们看到的SOC PI要求中“target impedance limits”其实就是在一段频率内的阻抗数值。

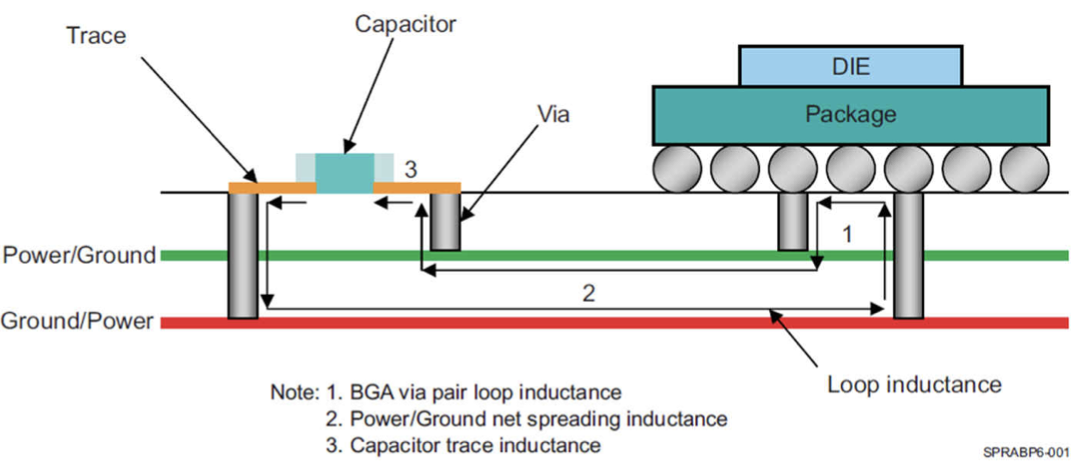

先从基本的概念去理解“阻抗”,Z0=√L/C,从公式上看电容越大,阻抗越小;电感越大,阻抗越大。所以AC部分的设计目标就是增大电容,减小电感。 这个问题从电容和电感的特性角度理解,电容可以储能,在网络需要能量时可以释放抑制电源网络的电压波动;电感在低频时表现为电阻,但在高频却阻碍电流的流动,所以看AC交流的部分是希望电感成分越小越好的。下面引用一张TI文档中的图片,PDN网络模型中有很多寄生电容及寄生电感,这些寄生参数的部分影响着PDN的性能。

图三 PDN网络等效模型

图三 PDN网络等效模型

结合上面图二可以看出来重点关注三个部分:VRM输出电容、PCB电源平面和IC去耦电容。

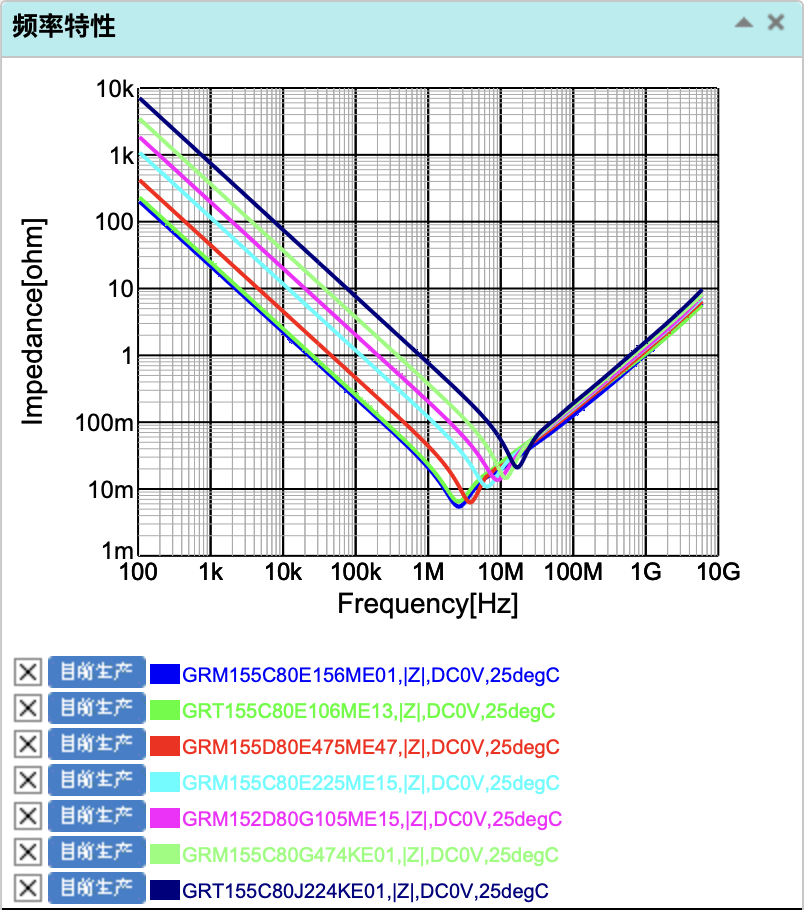

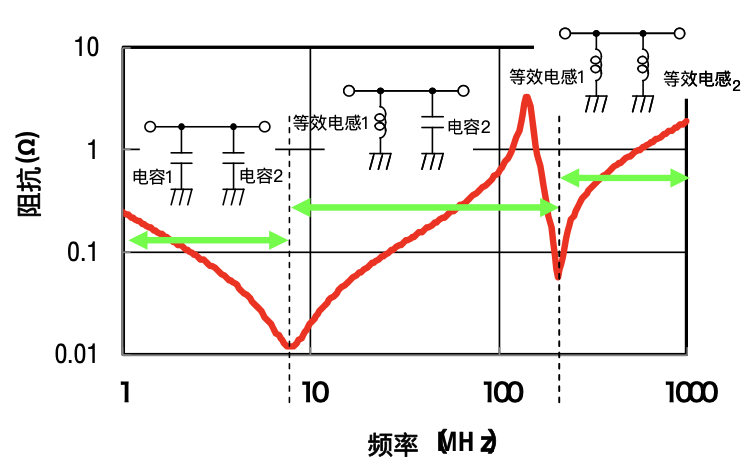

四、电容的特性在PI设计中是绝对的重点,了解电容的特性就能看出在PI没有达到要求时怎么去修改设计。如下图所示,GRM155系列0402封装的电容,容量越小的电容自谐振频率(阻抗最低的频率点)越大。当频率超过电容的自谐振频率后阻抗开始上升,电容开始呈现电感特性,开始阻碍电流变化。通常会使用多种相同容量(降低某一频段的ESR)和不同容量(扩展不同频段的ESR),电容并联会引入反谐振的问题,理论推导反谐振的阻抗趋向无穷大,阻抗变大的影响不仅仅是影响电源完整性,消耗的能量也会通过发热或者对外辐射的形式耗散掉从而引起EMI问题,参考图五示意。

图四 不同容量电容的阻抗曲线

图四 不同容量电容的阻抗曲线

图五 反谐振

图五 反谐振

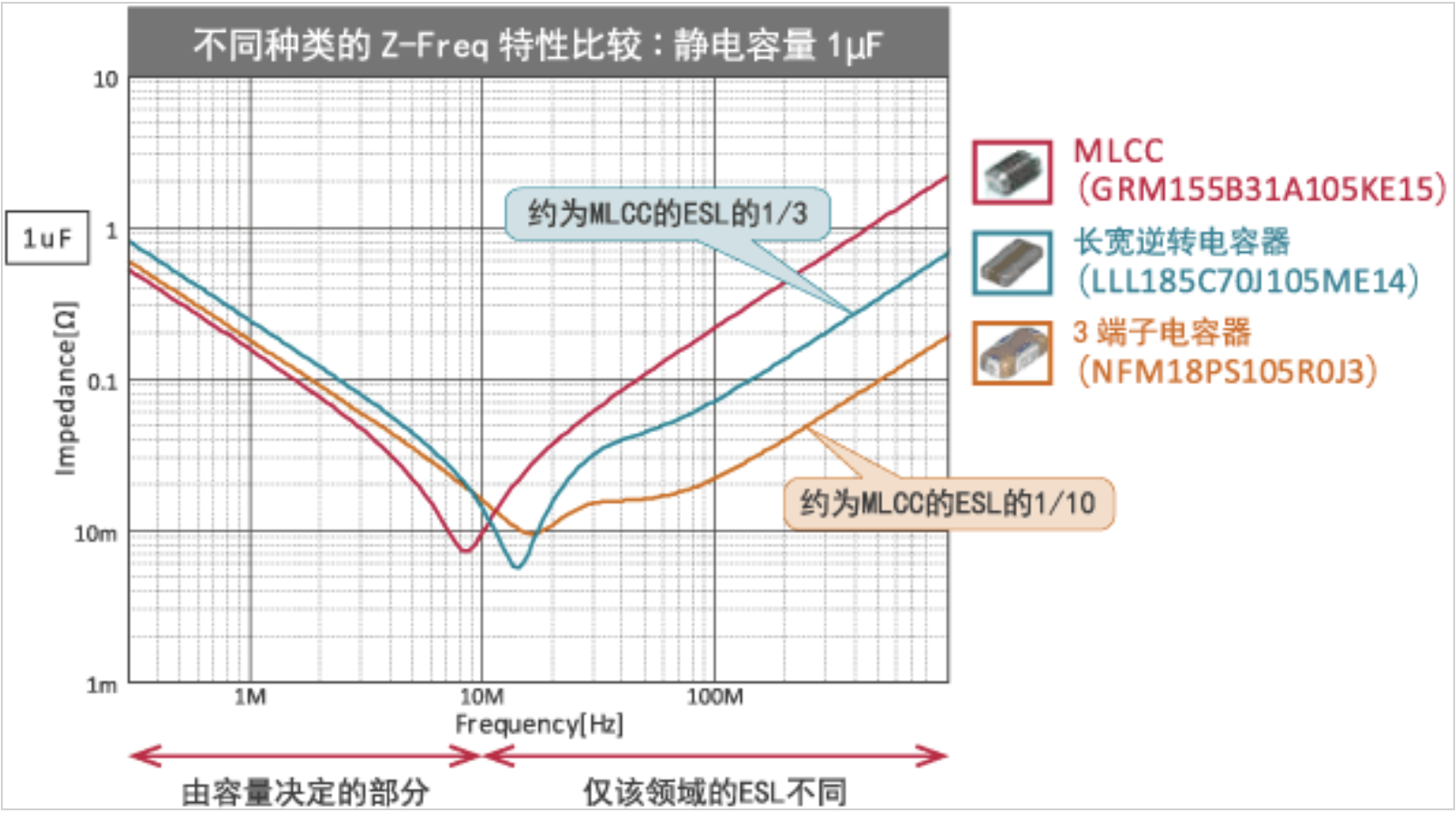

接下来还有两种特殊的电容,LW逆转型电容和三端子电容。同样容量的长宽逆转是MLCC的1/3;三端子是MLCC的1/10,因此在更高的频率上有更低的阻抗。还有一种IC封装常用到的“排容”,与排阻外观类似,同理也是缩小了引脚间距实现更低的ESL(LLA电容)。不局限于更高的频率,使用低ESL的电容也可以替代多个MLCC电容,实现更小的体积和空间占用。

图六 三种电容的阻抗曲线对比

图六 三种电容的阻抗曲线对比

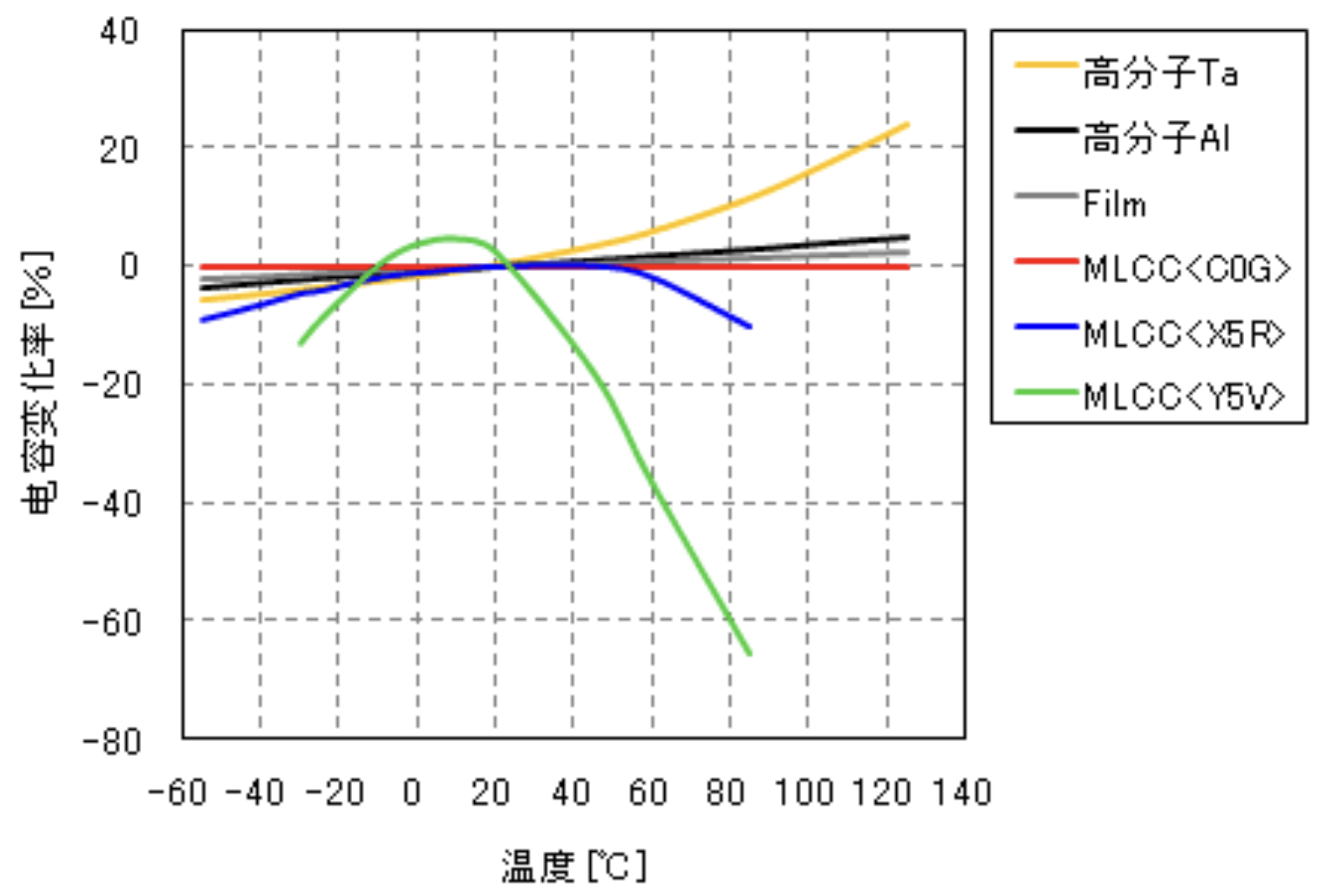

电容上还有一个不得不说的问题,那就是温度的影响;仿真的时候好好的,但高温下就会出现死机或者功能异常?这时候就是电容温度特性的原因(直流偏置&温度影响容值,温度影响ESL)。因此在选型和仿真的时候应该考虑不同的温度特性留出合理的margin(还有一点就是聚合物电容的电压降额问题-留坑④)。

图七 温度对电容量的影响

图七 温度对电容量的影响

五、电感从哪里来?有介质的地方就会有电容,有导体的地方就会有电感。PCB上所有导电的地方都会有寄生电感,这些电感阻碍电流变化,导致了电压波动,也就是电源噪声。

电容的ESL:从图四中就可以看出,当频率超过20Mhz之后不同容量的电容表现基本一致,这说明ESL是电容因素之外的影响,图四中电容均为0402封装,说明封装形式和大小对ESL影响是一致的,这也是尽量选择小封装电容的原因。除了电容本身封装的因素,电容的布局和布线也会影响ESL的大小。电容距离IC距离越近所形成的环路电感就越近(AC仿真(lumped&distributed),回路电感仿真-留坑⑤)。

图八 Layout寄生电感

图八 Layout寄生电感

六、平面谐振,这一部分研究的不多,没有遇到相关的问题。按照一些资料中的说法更多的考量是Power/GND平面以及介质形成的腔体除了寄生电容外还有寄生电感,当信号过孔穿越平面,同时没有很好的回流路径发散出的电磁波会与腔体内部产生谐振。另外一个是关注DCDC的输出阻抗与电源平面的寄生参数匹配引起谐振,影响DCDC控制环路稳定性(平面谐振频率+平面电容仿真-留坑⑥)。

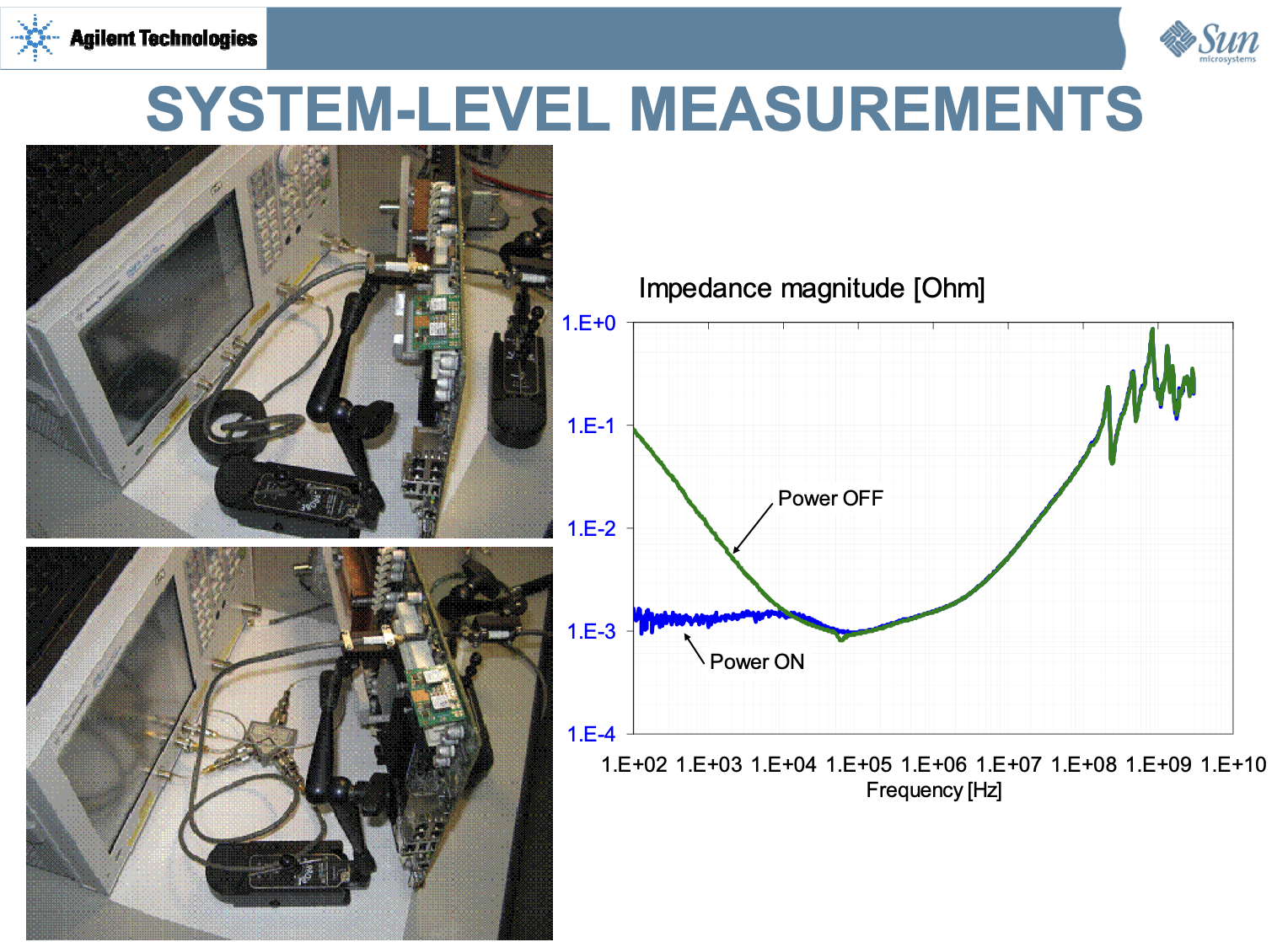

七、设计的工作结束了,坐等回板的时候思考了一下应该如何来测量仿真结果是否正确?

验证可以从两个方向来进行,第一个最直接,保持PCBA上元素和仿真时一致,直接使用VNA测量PDN的参数,和仿真结果做直接的对比。这部分工作我没有接触过需要参考Agilent文档: Accuracy Improvements of PDN Impedance Measurements

图九 PDN测量

图九 PDN测量

第二个就是间接的测量电源纹波(示波器,20MHz带宽限制,1X探头,最短接地环路),在IC端建立各种极端的抽载工况,从IC附近的去耦电容侧测量Voltage drop是否在允许的范围内,以及Voltage margin。借用下图示意测试方法。整体的测试需要从测试需求出发考量测试仪器性能及测试环境。比如示波器的带宽、采样率和ADC精度;测试线缆和探头的配置等。比如示波器输入阻抗对测试的影响,使用下图中同轴电缆测试时隔直电容的选择等。

更加暴力的方案就是不针对PI进行单独的测试,如果其他测试中未发现问题,直接进入EVT的可靠性摸底测试在不同的环境情况中看样机的功能表现,这个也是风险最大的。我们都知道项目中风险暴露点越晚,需要改进的代价就越大。

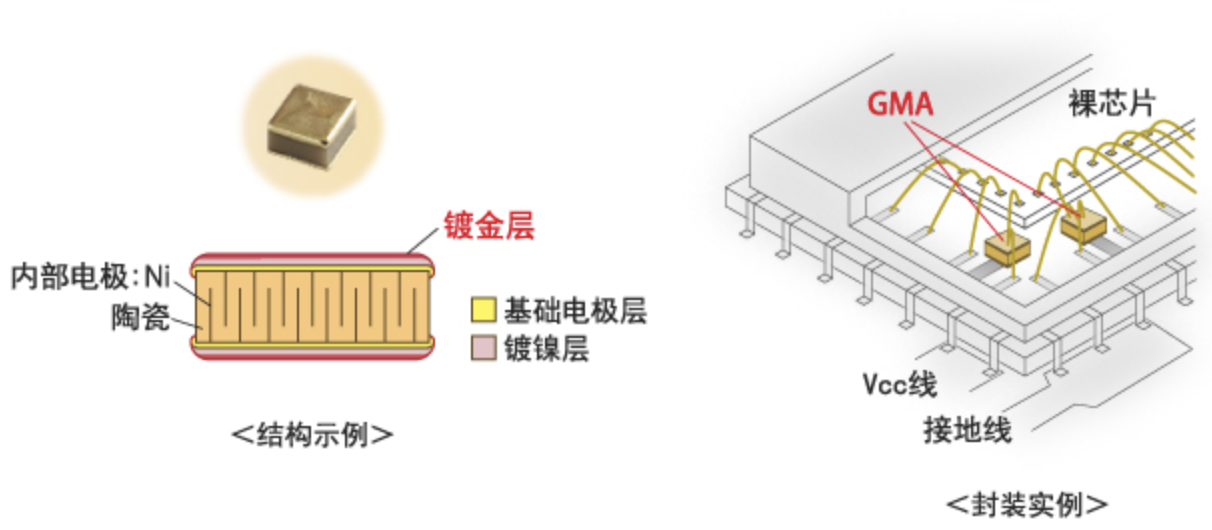

八、最后留一个最近的工作中引起的兴趣。SOC内部的PI是怎么处理的?SOC的集成度这么高的情况下也不可能塞MLCC进去。在muRata的网站无意中看到了一个特殊封装的电容,可以封装到IC内部。

图九 Wire Capacitors

图九 Wire Capacitors

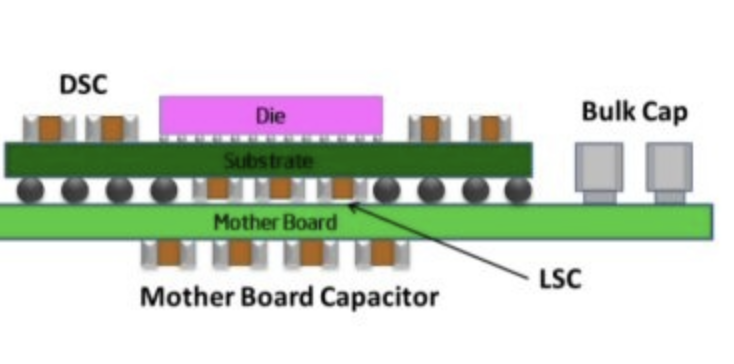

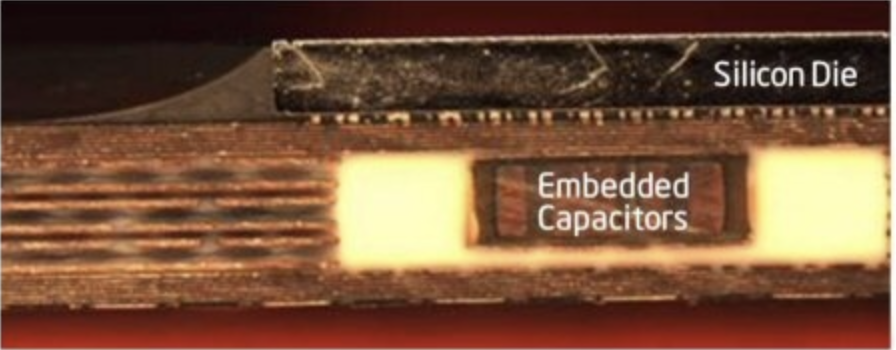

但相比上面的这个电容形式,另外几种在芯片Package应用上更常见一些:DSC、LSC和embeded capacitor。

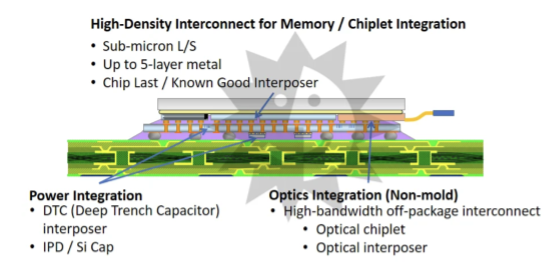

更高的频率还需要更特殊的处理,找专家咨询了一下,需要“Interposer中的DTC”以及SI CAP等Cdie来处理更高频的部分。找了张示意图,图中还有一部分关于Optical Chiplet和Interposer是示意。以后Chiplet也是一个重要的发展方向了,芯片的集成度将会越来越高。

结束。