1.IBIS

IBIS(Input Output Buffer Information Specification),是一种不需要披露具体电路设计,而是通过I/V数据给出DC特性,以V/t数据给出AC特性,以提供设备的输入输出接口特性的方式。可以想象成是一种基于“行为”建模的方式,适用于传输线和系统级别的仿真工作。所以IBIS是用来做和SI相关仿真的模型。

IBIS SPEC

由IBIS Open forum定义的规格信息组成。最早发布于1993年,目前已发布到IBIS ver7.2,规格书查阅下载地址。IBIS Spec定义了IBIS模型和文件的组成,以及格式和语法校验方法( ibischk)。

IBIS Model

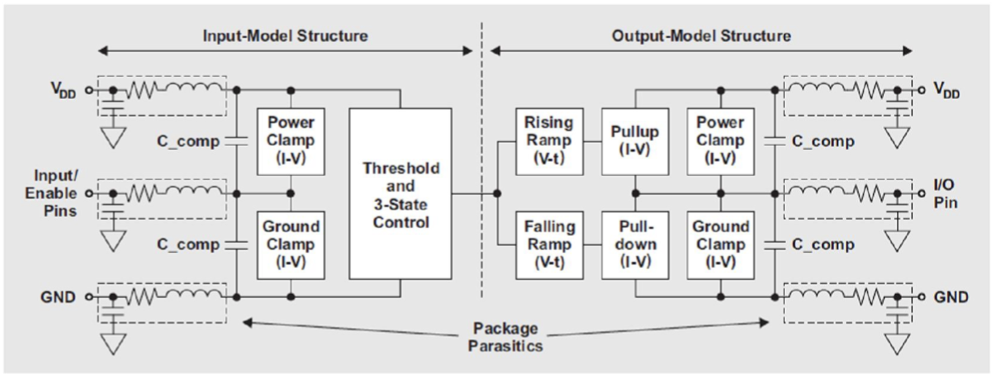

模型中包含了输入和输入两种不同的结构。模型包含了Package的寄生参数RLC和输入电容C_Comp;还有IC的工作DC电压信息以及保护的箝位电压信息;最后包含了芯片的输入特性信息I/V曲线表格,和芯片的输出特性V/t曲线表格。

IBIS File

偷懒,文件的格式解析就不写了,网上随手可以搜到。得看下版本,不同的版本内容定义会有变化。比较搞笑的时候,IBIS的版本更新有了新的特性会以BIRDs (Buffer Issue Resolution Documents)来发布。看起来IBIS和鸟的关系是脱不开了。文中开头的图片中的鸟是鹮IBIS。

Build IBIS

理解IBIS文件的来源有助于理解使用过程中所发生的和预期不一致的问题。通常IBIS的数据来源两个:基于仿真的方法和基于实际测试的方法。前者需要芯片的详细设计资料,比如原理图和封装的具体信息。这时候留下了一个坑,通过仿真的方法或者spice的方法转换模型会存在精度丢失的可能。所以拿到IBIS模型后还需关注是否准确反映了真实器件的行为。当然这部分验证需要实测或者是和spice对比仿真,一般都是芯片厂的工程师来完成。所以IBIS不意味着准确的代表了器件的行为,还需要结合实测来确保仿真的准确性。

2.IBIS-AMI

AMI的部分在IBIS ver5.0中引入,主要解决Serdes链路中无法再使用模拟链路完全代表器件行为的问题。高速串行总线的设计中为了达到更高的速率,在信号的发送和接收端应用了如FFE、DFE、CTLE等均衡设计。AMI(Algorithmic model Interface),.ami 文件描述了算法部分的能力和功能。我的工作中没有使用过这样的模型,留个坑以后用上了再补(Understanding IBIS-AMI Simulations)。

3.Pin delay

想起来写IBIS是因为一个群友问了一个关于Package delay的问题,刚好我也有这方面的疑惑。群友的问题:只拿到了IBIS模型和芯片的Pin delay信息,怎么把Pin delay信息加入到IBIS模型中来去仿真时序。最早我刚开始接触SI仿真的时候也有同样的困惑。

当时我的验证思路是搭建出一个完整的PCBA模型,然后尝试short PCB,对比PCB的延时是否会影响时序。结果是PCB short后时序完全错误,结果上来看IBIS已经包含了Package delay的信息了,否则两个IBIS直接怼一起应该是正确的时序结果。

这个事儿其实当时如果对IBIS的模型理解更加深入一些就不会有,当时拿到的IBIS模型中已经有每一个管脚的RLC信息了。Td=√LxC虽然只有一阶模型,但是对于一些频率没有超过5Ghz的应用来说已经够用了(一位大师的经验)。如果更高频的场景就需要S参数这样的频域模型来发挥作用了。这就是另一个验证方法,使用IBIS的RLC参数计算延时的结果,与IC的PIN delay事件做对比。

先按照1ps=6mil的大致转换算出DQ10的延时44ps。

Td=√LxC=√2.99e-9Hx1.23e-12F=60.644ps。

从大致的计算结果来看IBIS的RLC模型计算数值和package delay还有不少的差距,这块差异查阅了很多资料都没有提及。不过从Sigrity的仿真结果看是正确的,后面有机会能遇到sigrity的专家再去请教这个问题。